dolution

dolution.

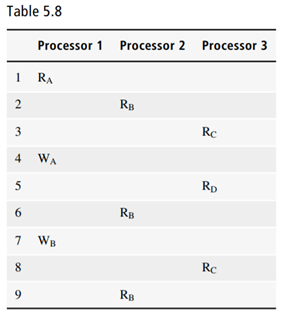

Consider a shared-memory multiprocessor that consists of three processor/cache units and where cache coherence is maintained by an MSI protocol. The private caches are direct-mapped. Table 5.8 shows the access sequence taken by three processors to four variables (A, B, C, and D), where A, B, and C belong to the same block and D belongs to a different block. The two blocks map to the same entry in the caches, and the cache is full initially.

Save your time - order a paper!

Get your paper written from scratch within the tight deadline. Our service is a reliable solution to all your troubles. Place an order on any task and we will take care of it. You won’t have to worry about the quality and deadlines

Order Paper Now(a) Classify the misses with respect to cold, replacement, true sharing, and false sharing misses.

(b) Which of the misses could be ignored and still guarantee that the execution is correct?

"Looking for a Similar Assignment? Get Expert Help at an Amazing Discount!"